Advancing Analog Design with AI: Sony AI’s Contributions at MLCAD 2025

Sony AI

September 9, 2025

Analog circuit design has long resisted the kind of automation that has transformed digital design. They may be small, yet mighty, but they are notoriously difficult to automate. While digital workflows have matured with standardized libraries and robust EDA (Electronic Design Automation) tools, analog still demands the meticulous efforts of experienced engineers, often requiring several days or even months to complete a single design task.

That variability is both the source of analog’s versatility and the reason it remains so dependent on human expertise.

At the ACM/IEEE International Symposium on Machine Learning for CAD (MLCAD) 2025, Sony AI is presenting two complementary research papers that address distinct but interconnected bottlenecks in the analog workflow:

GENIE-ASI: a training-free, two-stage approach for analog subcircuit identification that generates reusable Python code from a handful of examples.

Schemato: a fine-tuned large language model (LLM) that converts netlists into human-readable LTSpice schematics with high connectivity and layout fidelity.

Together, these works push forward the idea that LLMs can be embedded into analog design flows not as black-box predictors, but as collaborative tools that codify expert reasoning, automate tedious steps, and improve interpretability. And while each paper targets a different stage of the workflow—GENIE-ASI focuses on understanding circuit structure, and Schemato on making that structure visually interpretable—they share a common principle: designing AI methods that produce outputs engineers could directly use and trust.

GENIE-ASI: Generative Instruction and Executable Code for Analog Subcircuit Identification

Authors: Phuoc Pham (Technical University of Munich), Arun Venkitaraman (Sony AI, Switzerland), Chia-Yu Hsieh (Sony AI, Switzerland), Andrea Bonetti (Sony AI, Switzerland), Stefan Uhlich (Sony Semiconductor Solutions Europe, Germany), Lorenzo Servadei (Sony AI, Switzerland), Robert Wille (Technical University of Munich)

Why Subcircuit Identification Matters

Subcircuit identification is the process of finding functional building blocks (like current mirrors, differential pairs, inverters) within a larger analog design. It underpins downstream tasks like simulation, sizing, topology synthesis, and layout migration.

The challenge is variability, the researchers explain: many different implementations serve the same function. Rules that work for one variant may miss another. Templates cover known shapes but fail on new ones. Machine learning methods generalize better but, as the authors aptly note, “demand large, labeled datasets and often require extensive feature engineering.”

This is why the team investigated the feasibility of leveraging LLMs to identify subcircuits in SPICE netlists. They propose a novel approach — Generative Instruction and Executable Code for Analog Subcircuit Identification (GENIE-ASI) — harnesses the one- and few-shot capabilities of LLMs to perform subcircuit identification without relying on hand-crafted rules or large labeled datasets. As the researchers explain: “What distinguishes GENIE-ASI is its ability to generalize to unseen circuits with minimal supervision, even from a single example.”

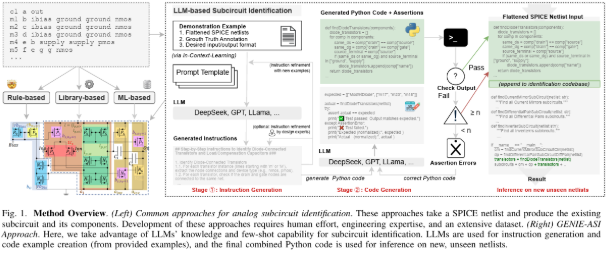

A Two-Stage LLM Workflow

GENIE-ASI sidesteps these trade-offs by treating subcircuit identification as a generative reasoning and code synthesis problem, executed in two stages:

- Instruction Generation: Given a small set of annotated SPICE netlists (sometimes just one example), the LLM produces a step-by-step natural-language procedure for detecting a subcircuit type.

- Code Generation: The model translates these rules into Python code for detection. The code is validated with assertion tests, and failures trigger an LLM-driven repair loop until the tests pass or a retry limit is reached.

-

This approach mirrors how engineers externalize expertise: first by articulating the reasoning, then by implementing it in reusable tooling.

A Benchmark Built for Diversity

Evaluating a subcircuit identification method on a handful of tidy examples can yield flattering results, but it says little about how the method will perform in the complexity of real design environments. To test GENIE-ASI under conditions that mirror actual engineering challenges, the team built a benchmark that goes far beyond previous studies.

Using the FUBOCO framework for op-amp generation, they created 300 synthetic operational amplifier netlists. This benchmark captures the heterogeneity that engineers regularly encounter:

Netlist sizes: from compact (<20 transistors) to large-scale (30–40).

Architectures: one-, two-, and three-stage op-amps; single-ended, symmetric, and fully differential.

Hierarchy levels (HL):

HL1 — device-level elements.

HL2 — structure-level groupings such as current mirrors or differential pairs.

HL3 — stage-level functional assemblies.

Each subcircuit type is represented by multiple variants (for example, six distinct current mirror topologies), ensuring that any approach must handle both familiar and less conventional configurations.

-

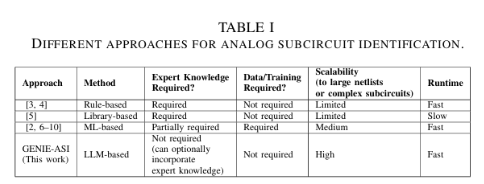

Comparison of rule-based, library-based, ML-based, and GENIE-ASI approaches in knowledge requirements, data needs, scalability, and runtime.

Results

Compared to baselines (Instruction + Following, Direct Prompting, Direct Code Generation): Instruction-first workflows improved precision and recall for HL1 and HL2. Code generation avoided token-limit issues and formatting errors common in large netlists. Performance parity with complex rule-based methods for HL1 and HL2, with no handcrafted rules or large datasets. HL3 remains challenging due to composite structures and strict cluster-matching criteria.

Significance

GENIE-ASI shows that LLMs can do more than answer prompts: they can produce robust, domain-specific tools. Once generated, the Python code can be applied to vast netlist libraries without further LLM inference, enabling scalable automation that adapts quickly to new subcircuit types.

Schemato: An LLM for Netlist-to-Schematic Conversion

Authors: Ryoga Matsuo (Sony AI, Switzerland / EPFL, Switzerland), Stefan Uhlich (Sony Semiconductor Solutions Europe, Germany), Arun Venkitaraman (Sony AI, Switzerland), Andrea Bonetti (Sony AI, Switzerland), Chia-Yu Hsieh (Sony AI, Switzerland), Ali Momeni (Sony AI, Switzerland / EPFL, Switzerland), Lukas Mauch (Sony Semiconductor Solutions Europe, Germany), Augusto Capone (Sony Semiconductor Solutions Europe, Germany), Eisaku Ohbuchi (Sony Semiconductor Solutions, Japan), Lorenzo Servadei (Sony AI, Switzerland / TU Munich, Germany)

Why Netlist-to-Schematic Conversion Matters

While GENIE-ASI focuses on understanding circuit structure, Schemato addresses the visualization gap. Netlists are exhaustive, but as the researchers explain, an analog designer usually views and assesses a circuit through the circuit diagram or schematics — not a netlist.

Manual conversion slows iteration and makes it harder for ML-generated designs to be evaluated by human experts. Previous automated approaches were constrained by heuristics, templates, or circuit-type specificity.

Translation as a Solution

Schemato reframes the problem as language translation: from netlist syntax to LTSpice .asc schematic syntax.

Development rested on three pillars:

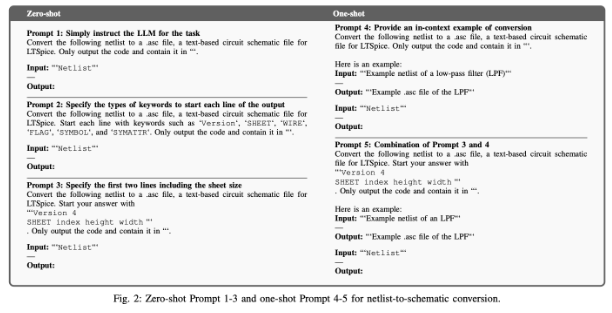

Prompt Engineering: From minimal task descriptions to syntax-specific prompts with LTSpice keywords, sheet size parameters, and one-shot examples.

In-Context Learning: Providing netlist–schematic pairs as guidance.

Fine-Tuning: Training a Llama 3.1-8B model on 44,995 augmented pairs for domain-specific accuracy.

-

Evolution of Schemato prompts from zero-shot minimalism to one-shot examples with explicit syntax and layout cues.

Dataset and Augmentation

The dataset began with 27,092 public LTSpice schematics, filtered to 10,428 unique designs.

Metrics and Results

On a 117-schematic test set, Schemato was evaluated with:

-Graph Edit Distance (GED) connectivity accuracy.

-Mean Structural Similarity Index (MSSIM) visual similarity.

-Compilation Success Rate (CSR) syntactic correctness in LTSpice.

-BLEU text-level similarity.

Results:

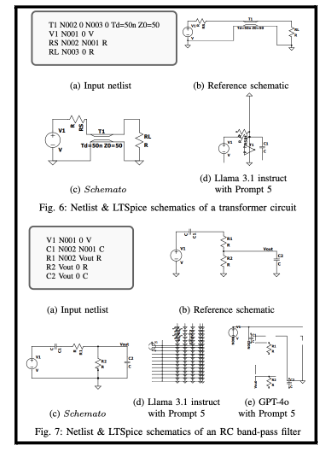

CSR: 76.07% vs. GPT-4o’s 63.25%.

GED (CSR-scaled): 0.27 vs. GPT-4o’s 0.15.

MSSIM (CSR-scaled): 0.17 vs. GPT-4o’s 0.04.

-

Reference and generated schematics for a transformer and RC band-pass filter. Schemato preserves topology and produces layouts close to the human reference.

-

Limitations and Future Work

Performance drops for circuits with >5 components or rare component types (appearing <10 times in training). The authors propose:

- -Expanding datasets with generic components.

- -Using mixup-style augmentation to combine smaller schematics into larger ones.

- -Decomposing large circuits into subcircuits before rendering.

Significance

Schemato eliminates a manual step, letting engineers load AI-generated schematics in LTSpice for immediate review. This shortens the feedback loop and makes ML-generated designs more accessible for expert inspection.

Conclusion

Together, GENIE-ASI and Schemato demonstrate how targeted use of large language models can close long-standing automation gaps without discarding the human expertise at the heart of analog engineering.

By designing workflows that produce verifiable, reusable outputs—whether executable detection code or production-ready schematics—these projects move beyond proof-of-concept and toward practical integration in real EDA environments. This is not AI replacing the engineer, but AI working alongside them: accelerating iteration, broadening coverage, and making design intent easier to capture and share.

As analog circuits continue to grow in complexity, the need for tools that combine adaptability, interpretability, and scalability will only increase. The research presented at MLCAD 2025 points to one path forward, where human insight and AI capability are woven into a more agile, collaborative design process. For Sony AI, these projects signal a broader direction: designing AI workflows that decompose complex design tasks into modular, verifiable steps, each producing assets engineers can integrate into their existing processes.

Latest Blog

March 5, 2026 | Imaging & Sensing, Sony AI

On Writing The Principles of Diffusion Models, A Q&A With Sony AI Researcher, Je…

IntroductionDiffusion models have become a go-to approach for high-quality generation; however, the field can be challenging to navigate once the paper titles and acronyms begin to…

March 2, 2026 | Sony AI

Advancing AI: Highlights from February

February at Sony AI was defined by momentum across global stages, research publications, and conversations about how AI moves from theory into practice.This month spanned responsib…

February 2, 2026 | Sony AI

Advancing AI: Highlights from January

January set the tone for the year ahead at Sony AI, with work that spans foundational research, scientific discovery, and global engagement with the research community.This month’s…